반응형

[엔지닉 X 인하대학교] 반도체 공정 실습 1일차 오후 수업 <반도체 공정 핵심 기술>

Chapter 1. 반도체 산업/소자 개요

반도체 산업

- 반도체 사업 구조

- Design (설계)

- Fabrication (전공정)

- Back-End (후공정)

- 전공정

- Wafer

- Deposition

- 포토 공정

- 식각 공정

- 이온 주입

- CMP

- 금속 배선

- 패키징 & 테스트

- 후공정

- Back Grinding(후면연삭)

- Wafet Dicing (절단)

- Wire Bonding

- Molding

- Package Test (Final Test)

- 기타

- 2023년 반도체 Keyword

- "수율, 생산성"

- 공정 미세화의 한계 : 미세화에 따른 성능 대비 공정 비용 증가 (파운드리 수율 비교 : 삼성 * 80%~, TSMC 80%

- 3차원 Integration : nMOS 위에 pMOS 구성, VTFET, CFET (3DSI) = 3차원으로 가니 공정이 어려워짐

- EUV Lithography : HiNA (0.55 → 0.7?) = 한번데 13nm, 그래서 노광을 많이 함 (지금은 NA가 0.33정도)

- 미국 Chip 4 동맹 본격 가동

- 전력 반도체 : 일본업체들의 선전

- AI Hardware (ChatGPT로 가속화)

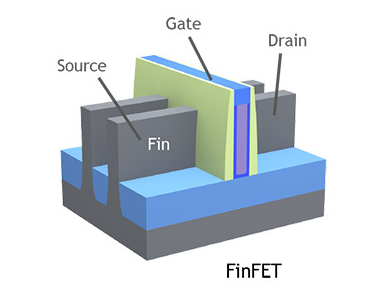

- Memory → MOSFET (DRAM → 3D stacked, Flash → 3D NAND) → system → CMOS → FinFET → GAA MOSFET

- "수율, 생산성"

1. 반도체 소자 개요

1. 실리콘(Silicon)과 게르마늄(Germanium)

- Si 원재료가 풍부하여 가격이 저렴하고 고품질

- 높은 온도(1,414ºC)의 녹는 점, 150ºC의 동작 온도 (Ge 100ºC)

- 반도체 제조에 필수적인 안정적인 산화막(Silicon Dioxide) 형성 = Channel 생성에 가장 중요한 것이 산화막임

- 반도체 : 2eV 이하의 물질

- 게르마늄은 실리콘보다 고속동작이 가능하지만 안정적인 산화막을 형성하지 않는다

- 왜 게르마늄이 더 빠를까? → 원자의 격자 구조

2. 고체의 결정구조

- Atomic Scale Structure of Materials

- 동일하게 똑같은 특성이 나와야 함 → 그래서 기판은 무조건 단결정

- Miller index : 결정구조의 결정면 (100)면 균일하고 소자 특성 확보가 가능하다.

- 원자 밀도가 모두 다름.

- 원자밀도가 높다 ? => 깎을 때는 시간이 오래 걸림(식각), 막을 만들때는 더 빠르게 수행 가능 (박막 증착)

3. 에너지 밴드

- 에너지 밴드 모델

- 교재 참고

- 에너지 밴드 다이어그램

- Fermi level : 전자에 의해 채워져 있을 확률이 50%인 에너지 준위

- Valance Band(가전자대) : 열평형 상태 T=0[K]에서 전자에 의해 채워진다. kT > 0, 전자가 전도 대역으로 빈자리를 정공이 채움

- Conduction Band(전도대) : T=0[K]에서 완전히 비어 있는 허용 에너지 대역

2. 도핑 (Doping)

- 반도체에 불순물을 조금만 첨가해서 반도체의 Band-Gap 특성을 크게 변화

- 주입 불순물 도펀트(Dopant), 종류 : Donor, Accepter 이온화

- Conduction Band 전자 생성 : 5족 Donor Ion

- Valance Band 정공 생성 : 3족 Accepter Ion

- n>p, n-type : majority carrier n, minority carrier p

- n<p, p-type : majority carrier p, minority carrier n

- Free electron(자유전자) : 공간에 정전기력과 반발력의 전하가 존재하지 않는 영역에서 전자의 이동이 제한이 없어 자유 전자

- 웨이퍼 만들 때 doping 해줌

- 불순물 doping의 농도를 다르게 해서 반도체를 도체 ~ 부도체로 만들 수 있음

3. PN 접합 (PN Junction), Diode

- PN Diode 전류

- Diffusion 전류 : 캐리어의 농도 차이에 의해 발생

- Drift 전류 : 외부 전계에 의한 캐리어의 표동

- 공핍층(Depletion Region)에는 Carrier가 존재하지 않아 Neutral Region의 Carrier diffusion current가 주요 Current Source (Majority carrier는 농도 차이가 너무 높아 공간의 농도 차이는 무의미)

- 순방향 바이어스에서는 Minority Carrier가 공간에 따른 농도(Concentration) 차이를 가짐 → PN Diode 전류는 Minority Carrier의 Concentration차이에 의한 "Diffusion Current"

- Total Current = Diffusion current + Drift Current

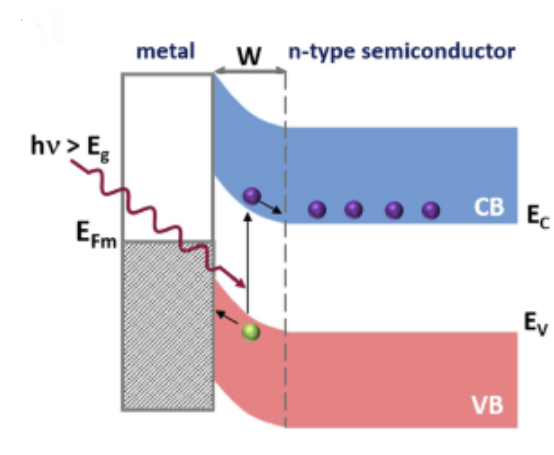

- Metal과 반도체를 붙이는 Schottky Junction Diode도 있음

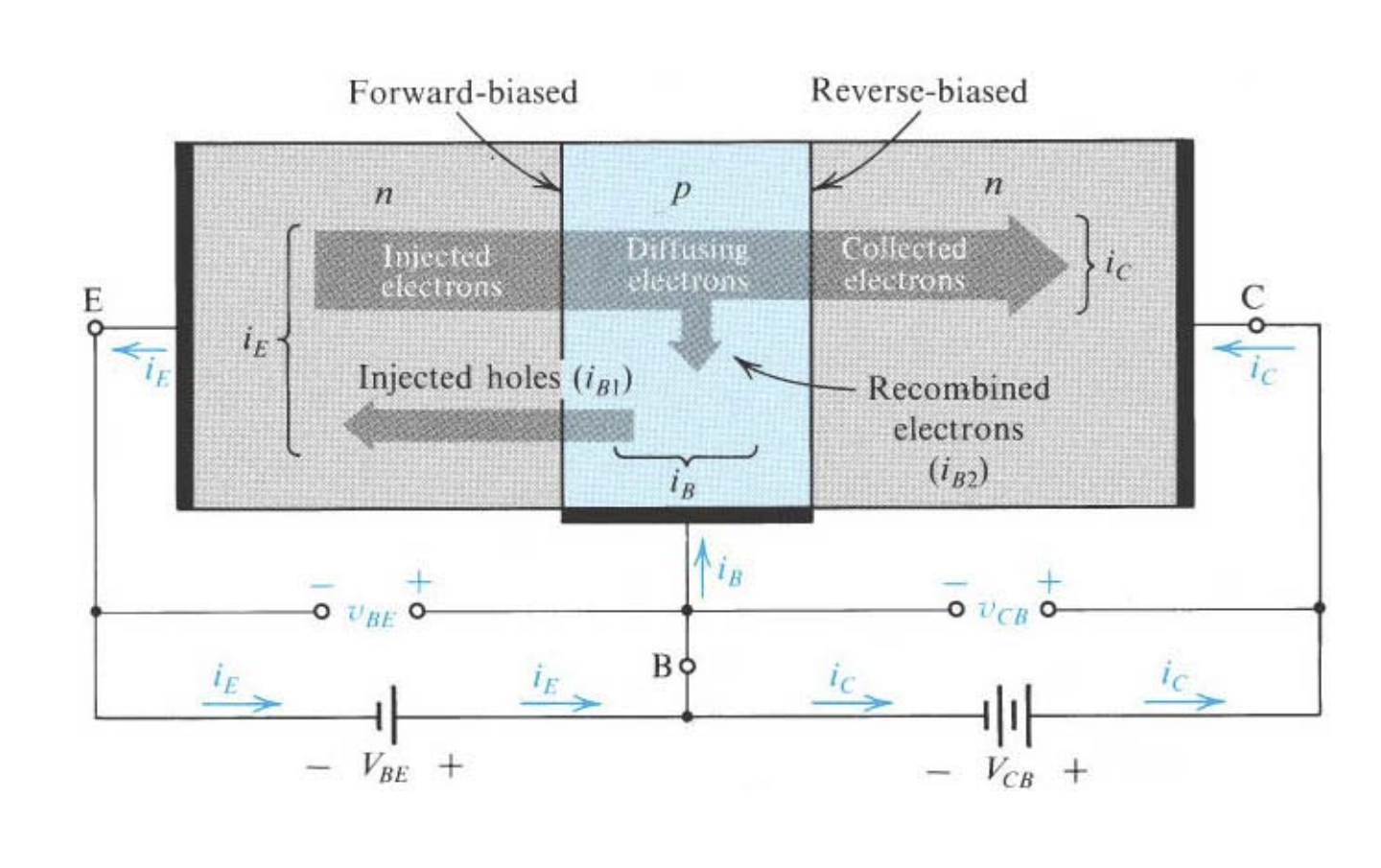

4. Bipolar Junction Transistor

- Transistor?

- 증폭

- 스위치

- 전류 구동

- 전력 증폭용으로는 사용 BUT 스위치로는 잘 사용 안함

- 다중 접합을 이용해 신호의 출력 전류 증폭이 가능한 3단자 소자

- 증폭 특성 : 조절용 베이스 전류 적고, 콜렉터 전류는 최대

- Carrier : Electron and Hole charge

- Amplifier, Oscillator, Filter, Rectifier and on-off switch

- 전류구동회로

- 열 발생률이 높음

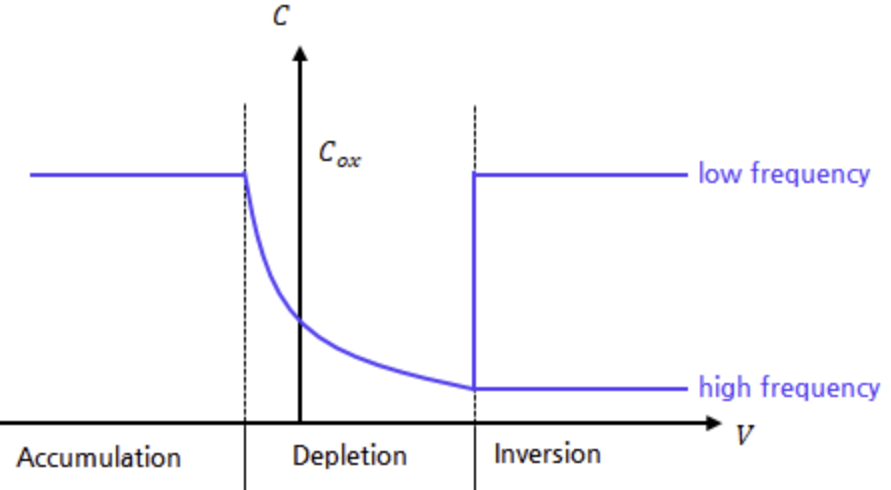

5. MOSCAP (MOS Capacitor)

- 축적 상태 (Accumulation), 공핍 상태 (Depletion), 반전 상태 (Inversion Mode)

- Threshold Voltage(문턱 전압 Vth) : Source와 Drain 간에 Conducting Path를 만드는데 필요한 최소 Vgs Voltage

- Accumulation

- hole이 차있음

- Depletion

- 공핍층 형성 (전압을 가해)

- Inversion Mode

- 전자가 빈자리를 채움 (hole 자리에 electron이 들어감)

- weak inversion / strong inversion으로 나눔

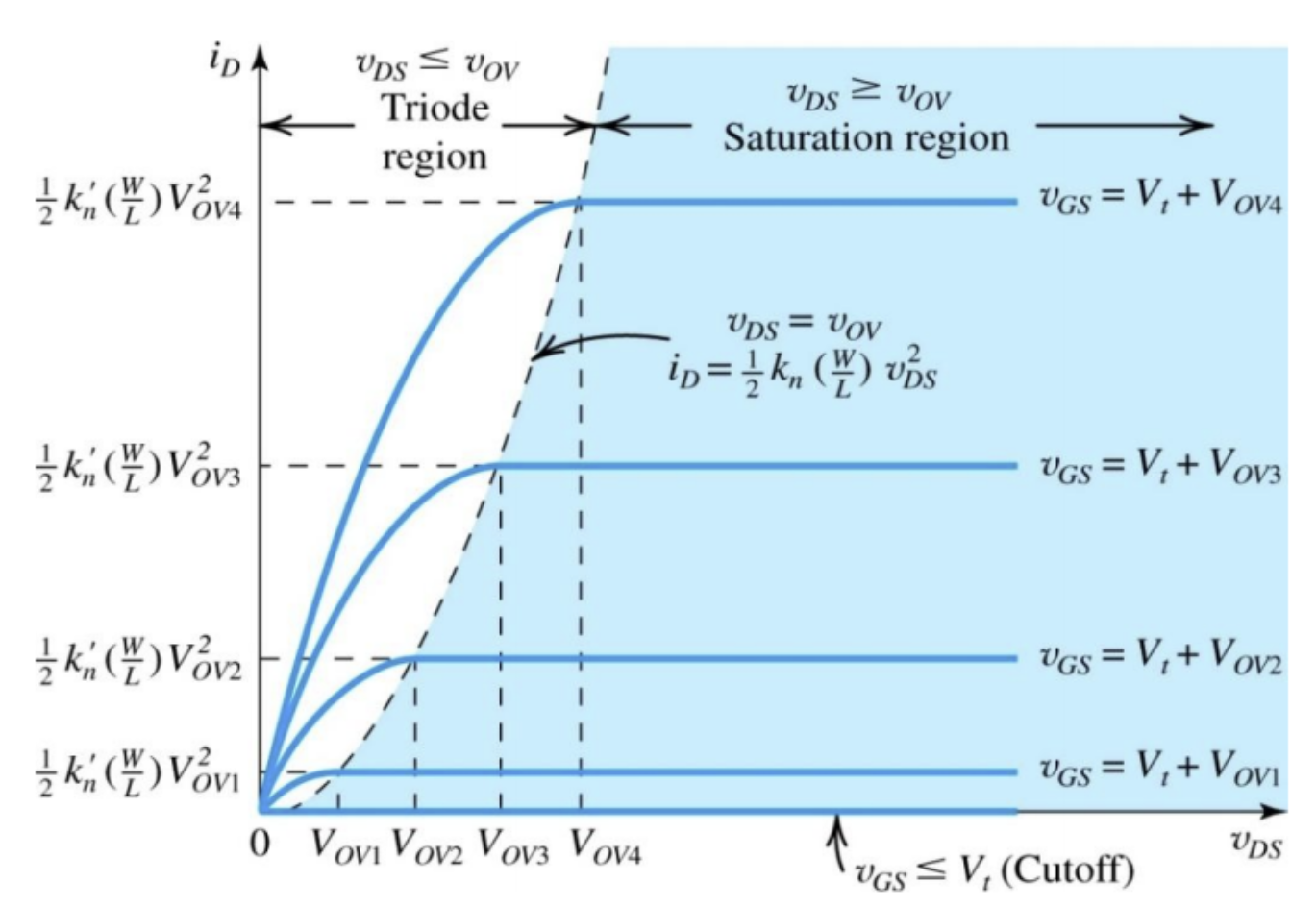

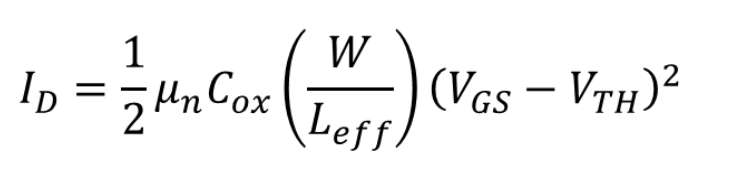

6. MOSFET

- Metal Oxide Semiconductor Field Effect Transistor (금속 산화막 반도체 전계 효과 트랜지스터)

- MOSCAP 반전 상태

- 전압 구동 회로 (Voltage Drive Circuit)

- Integrated Circuits (집적회로)

- On/Off를 하는 데 Gate 전압만 갖고 트랜지스터를 제어함 (전압은 열에 영향을 주지 않는다. 즉, 열 문제가 발생하지 않는다.)

- Long Channel Vs Short Channel

* 왜 Transistor를 축소할까?

- 집적도가 좋아짐 (작은 공간에 더 많이 채움, 가격, 수율)

- 동작속도가 빨라짐

- 전력소모가 작아짐 (배터리 수명 늘어남)

단점 ) 공정 상수율이 줄어듦, Short channel effect 문제 발생

반도체 집적도

- 진공관 → 트랜지스터 → IC → LSI → VLSI → ULSI

Chapter 2. Silicon Wafer

Silicon Wafer

- 전기적 요건

- p, n 타입과 같은 전기 전도성, Resistivity, Range, Radial Resistivity, Gradient, Resistivity Variation

- 기계적 요건

- 직경, 두께, TTV(Total Thicness Variation), BOW, Warp, Flat Dimension, Chips, Indent, Edge Counter, Bulk Structural Defect, Surface Orientation

- 화학적 요건

- Oxygen Content, Carbon Content, Oxidation-included Defect

- 표면적 요건

- Flatness, Particle Density, Haze, Sauce Pit

1. Polycrystalline Silicon

- 금속급 Silicon 제조는 환원 Arc 반응을 이용하여 규석으로부터 순도 98% 정도의 급속급 실리콘을 만드는 공정

- 실리콘 결정구조에서 Amorphous는 유리와 같은 비정질

- 전자의 이동도가 느려 주로 TFT-LCD 등에 사용

- Polycrystalline은 대부분의 다결정 박막에 사용

- Single Crystal은 단결정으로 실리콘 웨이펃에 사용

- Silicon Purification

- 순도를 초고순도로 만들어주는 과정

- Merallurgical process

- 2C(solid) + SiO2(solid) → Si(liquid) + 2CO(gas)

- 2,000ºC, 98~99% purity, Crude silicon or MGS

- Ultrahigh-purity Trichlorosilane(SiHCl3)

- Si(MGS) + 3HCI(gas) → SiHCl3(liquid) + H2(gas)

- 300ºC, 9s! purity

- Eletronic-grade Silicon process

- 2SiHCl3(gas) + H2(gas) → Si(solid) + 3HCl(gas)

- 1,100ºC, high purity polysilicon

- CZ(Czochralski) Growth Process (Pulling)

- 대부분 사용하는 방법

- Single-Crystal Silicon

- 다결정 실리콘 덩어리를 적층

- 결정 성장 챔버내의 가스를 모두 배출

- 결정 성장 중에 성장로에 활성 가스를 주입하여 대기중의 공기가 유입되지 않도록 한다

- Si의 녹는점, 1,412도로 가열하여 Silica를 녹인다

- 지름 5mm, 길이 100~300mm의 얇은 Seed를 액체 상태의 실리콘에 집어 넣는다

- Seed를 일정 속도로 회전 시키며 들어 올린다.

- CZ 단결정 성장 장치

- FZ(Float-Zone) Growth Process

- 순도는 굉장히 높지만 웨이퍼 사이즈는 한정적이어서 잘 사용 안함

3. Silicon wafer manufacturing process

- 8 major manufacture process steps

- Pulling

- Round Grinding

- Slicing

- Edge Rounding

- Lapping

- Etching

- Polishing

- Cleaning

Package Process

- Die Cutting

- Die Attach

- Wire Bonding

- Molding

- Marking & Forming

- Packing

Chapter 3. Fabrication 8대 단위 공정

1. Diffusion (확산)

- 확산은 농도 차이에 의해 입자들이 이동하여 평형 상태에 이르는 과정

- 확산 공정이란 웨이퍼에 특정 불순물을 주입하여 반도체 소자 형성을 위한 특정 영역을 형성

- 화학반응을 통해 형성된 물질을 웨이퍼 상에 다양한 형태의 막 형성

- 주요 확산 공정 (Furnace) : 산화막 성장, 폴리실리콘, 질화물 등

- 산화막 특징

- 우수한 전기적 절연체 (9eV 에너지 밴드 갭)

- High Breakdown Electric Field (10MV/cm으로 주변 전기장에 안정적)

- Si/SiO2 접합면의 우수한 특성

- Si 표면을 따라 산화막 성장 (Oxide Growth)

- 우수한 에칭 선택도

- Oxidation Reactions (산화 반응)

- Oxidation Reaction occurs at Si/SiO2 interface

- Si 내에서 Deal-Grove 모델로 불순물 재분포

- Silicon consume & interface move into Silicon

- 자연산화막 (Native Oxide) NH4F(에칭 속도제어) + HF (에칭)

- 제거해야함

- 건식 산화

- Dry Oxidation (Better quality)

- 소량, 많은 시간 소요 고가

- 품질이 우수함

- 습식 산화

- Wet Oxidation (Faster growth rate)

- 품질 저하

- 한번에 많은 양 가능 (대용량), 시간 단축이 가능하다, 저렴함

- 산화막 활용

- Implan/Diffusion Mask (Doping Barrier)

- 불순물 주입공정 등에서 불순물이 들어가지 않아야 할 곳 (Dopant Diffusion Barrier)에 마스킹 역할을 하는 아주 중요한 기능

- Device Isolation (소자 분리)

- 트랜지스터간에 원치 않는 전류가 흘러 Tr이 계획되지 않았던 오동작 발생

- 절연 물질을 Tr 사이에 채워 넣는 소자 분리 방법

- Tr과 Tr 사이에 위치를 선정하고 두꺼운 절연막을 형성시켜 이웃한 Tr이 서로 전기적으로 연결되는 것을 차단

- 플라즈마 상태를 이용해 건식(Dry) 식각 방식 사용

- LOCOS (Local Oxidation of Silicon 실리콘 부분 산화법)

- 반도체 기판에 형성된 패드 산화막과 질화막을 패터닝한 후 선택적 산화 공정에 의해 소자분리막을 형성하는 공정

- 장시간 고온 산화로 인하여 채널 저지 이온의 측면 확산 및 측면 산화에 의해 소자의 전기적인 특성을 저하시키는 원인으로 작용하는 버즈 빅이 발생

- 약 0.25um 이하의 공정에는 적용의 한계

- STI (Shallow Trench Isolation)

- 반도체 기판에 일정한 깊이를 갖는 트렌치를 질화막 또는 질화막 + 산화막을 마스크로 이용하여 형성

- 트렌치에 절연 물질을 매립시킨 후 CMP 공정에 의해 매립된 부분을 제외한 절연물질을 제거함으로써 소자 분리막을 형성

- 반도체 소자의 스케일링(scaling)에 유리하고 절연 특성이 양호

- Nitride mask 제거 (Etching by Phosphoric Acid, H3PO4)

- Gate 절연막

- 전자의 이동을 차단하는 역할

- 게이트의 전압 민감도를 결정

- 두꺼운 막의 장점 : 전자 보관성, 절연 내구성, 누설전류 차단

- 얇은 막의 장점 : 동작 속도, 전력 소모, 칩 축소

- 전기적 절연 및 유전 Multilevel Interconnector (ILD)

- Implan/Diffusion Mask (Doping Barrier)

- 산화막 형성

- Thermal Oxidation (열산화)

- 800 ~ 1200ºC의 고온 챔버 사용, 보편적 방법

- 산소와 수증기를 반응체로 사용

- 산화막 성장 속도가 빠르고 보다 두꺼운 막을 형성 (열을 가해줌)

- 산화막 Parameter : timing, temperature, gas flow

- Dry Oxidation (건식 산화)

- 산화막 성장 속도가 느려 주로 얇은 막을 형성할 때 사용

- 성장 속도가 느릴수록 막의 두께를 조정(control) 용이

- 건식 산화는 전기적 특성이 좋은 산화물

- Dummy Wafer : 온도와 가스의 균일도 확보

- 동일한 챔버 안에서도 온도가 동일하지 않음! 양쪽의 7장 정도씩 Dummy(못쓰는) wafer 발생

- 산화막 성장 모델

- Grow an oxide layer of thickness t

- Oxide 두꼐 : 0.45t 실리콘 원자가 웨이퍼에서 소모

- charge trap 방지 (안생김)

- 산화막 성장률

- Time

- Wafer orientation

- Dopant Effects

- Pressure

- 계면 포획 전하

- Si, SiO2 경계면에서 결합하지 못한 Si 원자에 의해 형성 (Dangling bonds)

- 양전하 또는 음전하

- [100] 결정면 계면포획전하는 [111]결정면 방위면에서 보다 더 작은 값을 가짐

- 계면 포획전하의 증가는 MOSFET소자의 문턱전압 변동을 유발

- 표면에서의 전하의 이동도를 저하시켜 소자의 특성 저하를 유발

- Thermal Oxidation (열산화)

2. Deposition (증착)

- 반도체 소자를 만들 때 사용되는 금속층간 유전체(절연) 및 금속(전도) 재료 층 및 반도체층을 형성 트랜지스터

- 재료 유형과 형성 구조에 따라 다양한 기법이 사용

- 실리콘 관통 전극(TSV)과 웨이퍼 수준의 패키징(WLP)에는 구리와 기타 금속의 금속 도금도 사용

- 텅스텐 커넥터와 가는 보호막은 한 번에 단 몇 개의 원자 층을 추가하는 정밀한 화학 증기 증착(CVD)과 원자층 층착(ALD)을 통해 형성

- 증착 균일도, 필름 응력 제어 및 결함도를 개선하는 고성능 장비로 높은 처리량과 낮은 관리 비용 요구

- 박막품질특성 (Deposition Quality Characteristics)

- 박막 균일도(Film Uniformity) : 종횡비 (Aspect Ratio), 갭 필(Gap Fill) 균일도

- 전기적 특성 : 전도율 (Conductivity)

- 물리, 화학적 특성

- 기계적 특성 : 박막의 응력, 접착력 (Adhesion)

- 결함 : 핀홀 (Pinholes), 단차 피복성 (Step coverage)

- 불순물 : 오염 (Contamination)

- 광학 특성 : 반사도 (Reflecitivity)

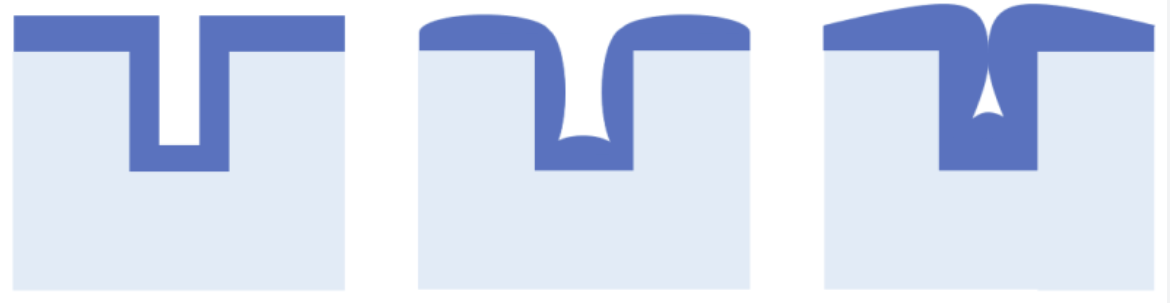

- Step coverage

- 코너 부분이 먼저 쌓여 안쪽까지 쌓이지 않는 경우

- SC = Film thickness on the side of a step / Thickness on the Horizontal surface

- Thickness Uniformity

- 두께가 일정해야 하는데 일정하지 않는 등의 문제

- Precise thickness control

- Pinhole free films

- High aspect ratio materials

- Uniformity on a flat surface

- Thin Film Purity

- Adhesion

- Stress

- 금속에 열을 가했다 식으면 축소함 → 문제됨

- Tensile stree : Bend upward

- Compressive stress : Bend downward

- Deposition Technology

- Chemical Vapor Deposition (CVD)

- Low-Pressure CVD (LPCVD)

- Plasma-Enhanced CVD (PECVD)

- HDP(High Denity Plasma)

- Atmospheric Pressure CVD (APCVD)

- Metal Organic CVD (MOCVD)

- Atomic Layer Deposition (ALD)

- Physical Vapor Deposition (PVD)

- Thermal evaporation

- E=bean evaporation

- Sputtering

- Molecular Beam Eqitaxy (MBE)

- Oxidation

- Spin-on Film coating

- Electro-chemical deposition

- Chemical Vapor Deposition (CVD)

- Plasma Formation

- 진공 챔버의 반응 가스에 강한 전기장 인가, 챔버 내의 전자가 가속되어 열전자

- 음극에서 방출된 열전자와 중성가스 충돌로 이온화 반응

- 연쇄적 이온화 반응으로 플라즈마 상태 유지

- 여기 반응없이 Dark Space인 Sheath 영역의 전위 변화

- DPP(Discharge Produced Plasma) : 특정한 물질 환경속에서 전극간에 대전류 펄스를 흘려 Plasma 발생

- LPP(Laser Produced Plasma) : 특정 물질에 강한 레이저 광을 집광하여 Plasma 발생 ex) EUV

- DC Plasma VS RF(AC) Plasma

| DC Plasma | RF(AC) Plasma |

| - 두 전도성 전극 사이에 기체 주입 - 초기 DC 방전으로 Plasma 발생 - 전극이 직접 Plasma와 접촉 - 전도체만 가능 (절연체의 유전분극발생) |

- RF 대역의 AC 전원 사용(13.56MHz) - 양이온과 전자를 교대로 당김 - 외부전극사용(부식, 오염 방지) - DC Plasma 보다 이온화율 높음 - Z Matching Controller - 전도체, 절연체 모두 가능 |

- 물리 기상 증착 (Physical Vapor Deposition, PVD)

- Physical method : atom that deposit on substrate

- Low temperature deposition

- Vacuum deposition : done in evacuated chamber

- Common PVD processes : Sputtering and Evaporation

- Sputtering

- High deposition rate

- High purity thin film (vacuum, low pressure)

- Good adhesion, step coverage and uniformigy

- DC 스퍼터링 (ex. Metal) 및 RF 스퍼터링 power (ex. Insulator)

- 챔버 내에 충분한 농도의 반응가스 주입, DC 300~5,000V로 플라즈마 형성, 가스 원자(Ar)가 이온화, 이온이 가속으로 Target 금속과 충돌로 Sputtering

- Thermal Evaporation

- 열증착법(Thermal Evaporation)은 증착 물질을 보트 위에 두고 가열

- 증착 물질을 증발시켜 웨이퍼에 증착하는 방식

- 고진공을 사용하므로 진공 증착 (Evaporation)이라고도 부름

- 화학 기상 증착 (Chemical Vapor Deposition, CVD)

- System

- Gas Delivery System

- Reactor Chamber

- Substrate Loading Mechanism

- Energy Source

- Vacuum System

- Exhaust System

- Process Control Equipment

- Energy Source

- Thermal

- Plasma

- Laser

- Photons

- 상압 화학 기상 증착 AP(Atmospheric Pressure) CVD

- TEOS(Tera Ethyl Ortho Silicate) + Ozone O3 → SiO2

- 저온 공정 (400~500ºC)의 온도 제어 용이하여 균일한 증착 속도 달성

- 낮은 반응 속도로 웨이퍼 처리량 (Throughput) 저하

- Typical coating thicknesses range from 10 to 1000 nm.

- 외부 에너지 사용 안함 → 웨이퍼 처리량은 떨어짐

- Oxide deposition

- Low Uniformity

- Particle contamination

- SiO2

- BPSG (Passivation) → thermal reflow 하면 액체가 됨 → 평평해짐

- 저압 화학 기상 증착 LP(Low Pressure) CVD

- 0.1 ~ 10 torr의 저압 및 High Temp. 550 ~ 900ºC

- 증착 속도 제어에 민감하여 APCVD에 증착 속도 느림

- Wafer is exposed to one or more volatile precursors

- Excellent purity, uniformity and step coverage

- 진공 챔버 사용

- Silicon Dioxide : TEOS(낮은 압력, 기체 입자의 급록한 표면 확산으로 우수한 막), SiH4(450도의 낮은 온도, Step coverage 빈약)

- Silicon Nitride(SiN)

- Si3N4

- Poly Silicon

- W (Tungsten)

- SiO2

- SiGe epitaxial films

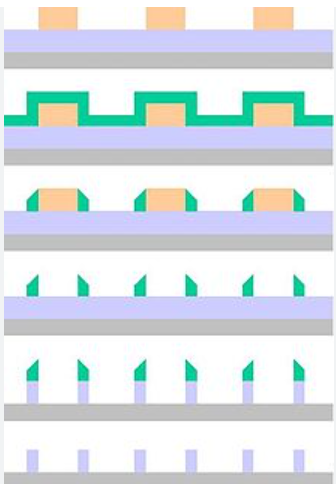

- 플라즈마 강화 화학 기상 증착 PE(Plasma Enhanced) CVD

- 낮은 온도에서 박막 형성 가능 (200 ~ 500ºC)

- 낮은 공정 온도, 다양한 공정 변수 조절로 박막 특정 조절

- 반응 에너지원으로 열이 아닌 플라즈마의 활성종(Radical) 사용

- 높은 웨이퍼 처리량 및 우수한 기계적 특성

- Step Coverage : LPCVD > PECVD > APCVD

- Plasma can cause wafer surface damage

- Poor gapfill capability → HDP CVD (가스를 사용하기 때문에 발생하는 문제)

- PECVD Reaction Process

- 반응 챔버의 진공상태에서 RF 에너지가 가스 분자를 분해시키고 플라즈마 형성

- 플라즈마 상태에서 가스와 함께 주입된 반응물 (Reactants)들은 RF 전기장에 의해 분리

- 분리된 반응 분자들은 새로운 전구체(Precursor)를 형성

- 형성된 전구체들은 막이 증착되어지는 웨이퍼에 흡착

- 흡착된 전구체는 웨이퍼 안으로 확산

- 웨이퍼에 가한 열로 새로운 막을 형성

- 웨이퍼와의 계면에 일차적인 Seed 원자층이 형성

- 원자층 위로 규칙적인 결정 구조를 유지하면서 원하는 두께까지 막이 형성

- 진행되는 동안 반응에서 분리된 분자들은 새로운 휘발성 가스를 형성, 진공 펌프에 의해 배기층으로 배출

- HDP (High Density Plasma) CVD

- PECVD 보다 저압에서 ICP 고밀도 Plasma를 형성하여 막을 증착

- 고종횡비(HAR)에 선호되는 공정

- 박막 증착과 스퍼터링 식각을 동시에 진행

- Depo-Etch-Depo-Etch-... Gap Fill 특성 우수

- 얇은 트렌치 소자 분리(STI)

- 층간 유전체(ILD)

- 금속 층간 유전체(IMD)

- 식각 보호막

- System

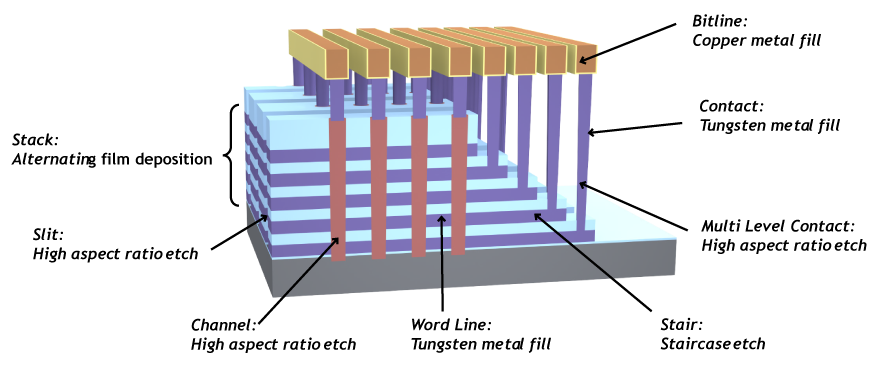

- Thermal Atomic Layer Deposition (ALD, 원자층 증착법)

- 기판의 모양에 상관없이 얇고 균일한 박막 형성이 가능

- 원자 수준의 두께의 얇은 막을 형성하는 방법

- Deposition deep trench structure (ex. DRAM Capacitor, High-k)

- 전구체 선택에 따라 상이한 박막 연속 증착 가능

- 자기포화반응 (Self Saturated Reaction)

- Low temperature Deposition (저온 증착 공정)

- 3D 구조가 복잡해지면 ALD 방법 말고는 방법이 없음

- 왜 ALD 공정이 많아지는가?

- 일정한 두께로 박막 증착

- 세로로 긴 상태면 ALD 방법 말고는 없음

- 이런 구조도 ALD 밖에 방법이 없음

- ALD Self-limiting Surface Reactions Cycle & PEALD

- Precursor dose

- Purge (Removal Byproduct)

- Reactant dose

- Purge (Byproduct)

- 1 Cycle (1~2nm)

- 1 Cycle 거치면 원자층 1층이 만들어진다 → 1~2nm

- PE(Plasma Enhanced) ALD

- Fast deposition

- Lower temporature

- ALD Conclusion

- CVD는 전구체와 반응체를 같이 주입

- ALD는 전구체와 반응체를 분리 주입

- III-V MOSFET for future CMOS Logic Technology

3. Photo Lithography (노광)

- Reticle (Photo Mask)

- 도면 검사까지 마친 레이아웃(Layout) 패턴을 E-Beam를 통해 순도가 높은 석영을 가공해서 만든 유리판 위에 그려져 MASK(Recticle)로 제작

- Glass 재질로 Fab 공정의 크롬이 도포된 석영 유리(Quartz) 및 Bumping 공정의 Sodalime 2종료

- Mask defect & repair

- Protrusion : extra chrome attached to a feature

- Intrusion : partial loss of chrome in a feature

- Bridge : chrome connecting two features

- Necking : discontinuity in a line

- Pinhole : hole in a chrome

- Pin spot : extra chrome on a light field area

- Photomask Alignment

- 마스크는 여러 장을 사용하므로 웨이퍼와의 정렬이 필수

- 하나만 잘못되어도 안됨

- Align Key(보통 + 모양)에 맞추어 설계대로 제작 가능

- Mis-align의 경우, 재작업 진행

- Resolution Enhancement Technology (RET)

- 1. OPC (Optical Proximity Correction)

- 광학 근접 보정(OPC) : Mask with Serif, Mousebite, Hammerhead

- 회적 효과가 작용, 빛이 마스크에서 웨이퍼로 통과함에 따라 빛의 파동이 확산되고 간섭이 수반됨

- Deep Learning 알고리즘을 이용한 Model 기반 패턴 기술 이용

- 해상도는 작을수록 좋음 (더 미세한 해상도 볼 수 있음)

- 2. 변형조명법 Off-axis illumination(OAI)

- NA를 증가시키면서 DOF(Depth of Focus)를 높이는 광학적인 방법

- Pattern의 정보를 담고있는 1차광이 최대한 Lens 내부로 많이 들어가도록 설계 0차와 -1차만 집광하여 DOF를 높이는 기술

- Pattern size가 줄게 되면 Reticle에 의한 회절각이 커져 1차광 손실

- OAI에서 0차광을 경사지게 입사시켜 Reticle에 의한 회절각이 커져도 -1차광이 Lens 속으로 안정적으로 들어감

- 초점심도는 높을수록(깊을수록) 좋음

- 초점심도를 높이면 해상도가 커짐

- 회사 입장에서는 미세 패턴을 만들어야하니 큰 렌즈를 쓰고 싶고 엔지니어들은 조절하기 쉬우려고 작은 렌즈를 쓰고 싶어함 → 그래서 나온 것이 변형조명법

- 3. Annular illumination (AI)

- 광선의 일관성을 조절하면 회절과 산란 현상을 억제하여 간섭 무늬를 어느 정도 제거

- "Black Disk"에 의한 빔의 단면 차단 조절

- 광선의 단면 내부를 광학적으로 가리면 광선의 일관성을 조절 가능

- 리소그래피의 성능을 최적화하여 보다 선명한 선 폭의 이미지를 인쇄하는 방법

- 4. Phase Shift Mask

- 패턴의 미세화로 회절과 산란 현상에 의해 선 폭 주변에서 간섭으로 패턴이 왜곡되는 현상 발생

- PSM은 빛의 세기 및 위상을 조절하여 원치 않는 회절광의 간섭 효과를 없애 제거하는 방법

- 1. OPC (Optical Proximity Correction)

- Photoresist

- Photoresist (감광성 고분자) : 특정 파장의 빛에 의해 분자구조가 바뀌어 용해도가 변하는 물질

- 두꺼운 PR : Aspect Ratio 패턴 문제

- 얇은 PR : Etch 내성 부족 → Hard mask 필요 (SiON막 등 사용)

- Developer : Alkaline + DI Water, 2.38% TMAH

- 1. PR Coating Comparison

- Spin coating

- Spray coating

- ED coating

- 2. Positive & Negative Resist

- Positive photoresist : high aspect ratio (대부분 사용, 빛을 받은 부분 제거)

- Negative photoresist : Lift-off (빛을 안받은 부분 제거)

- Photolithography Technology

- Photolithograpy Track System

- Pre-bake

- Primer Vapor

- PR Coating

- Soft-bake (빛이 안들어갈 정도로는 하면 안됨)

- Alignment & Exposure

- Post Exposure Bake

- Development

- Hard-bake

- Pattern Inspection

- 20 ~ 30번의 공정 과정을 거침

- Photolithograpy Track System

- Advanced Lithography

- Photolithography Limitations

- Light source : Little "deep UV" spectra

- Require shorter wavelength light source

- Photoresist sensitive to appropriate wavelength

- Lens and optical components limit numeric aperture

- Next Generation Lithography

- Multiple Patterning Lithography

- Extreme UV Lithography (EUVL)

- Photolithography Limitations

- 다중 패터닝 (Multiple Patterning)

- ArF imersion 노광 기술의 미세 공정 한계가 약 30nm로 제한

- 단일 패터닝의 결과 pitch사이 추가적인 패턴을 형성하고자 하는 방법 (Pitch splitting technology)

- 미세화에 따른 밀도 높고 복잡한 형태의 패턴을 형성하기 위해 사용하는 방법

- 공정이 반복되는 과정에서 Overlay issue, 즉 마스크 충돌의 정렬 상태가 고르지 못하여 여러 문제들이 발생

- 공정의 횟수가 늘어나기 때문에 생산성은 싱글 패터닝보다 떨어지며, 공정의 증가로 인한 다른 비용들도 증가

- Double Patterning Lithography

- ArF 이머젼 공정 한계 : 36nm

- 메모리 셀 어레이의 규칙적인 패터닝에 적합

- LELE(Litho-Etch-Litho-Etch) : Print twice, 30% reduction in pitch, 22nm, overlay error, CMOS Logic & system ICs, EUVL

- 자기 정렬 4중 패터닝 SADP(Self-Aligned Double Patterning) : 1xnm node, Memory Devices (ALD 적용)

4. Etch (식각)

- 회로 패턴 구성을 위해 물질의 선택적 제거

- 식각 공정에서 물질의 실수로 제거되면 바로잡기 어려움

- 부정확하게 식각된 웨이퍼는 기능 상실로 폐기

- 공정 전체의 약 70%가 Etch 기술 필요

- Isotropic(등방성) vs Anisotropic(비등방성)

- Dry(건식) vs Wet(습식)

- 1. Etching Materials

- Dioxide : 불산(HF), 완충불산(Buffer HF)

- Isotropic Silicon / Poly-silicon : 질산(HNO3 : 실리콘 산화), 불산(HF : 형성된 산화막 제거)

- Anisotropic Silicon : 수산화 칼륨(KOH), TMAD, EDP 혼합물

- Nitride(Si3N4) : 인산

- Aluminum : 강산 혼합용액 (질산 : 알루미늄 산화, 인산 : 산화 알루미늄 분해, 아세트산 : 질산의 산화를 저속 반응으로 조절)

- Titanium (Silicide) : 과산화수소(H2O2)와 황산(H2SO4)의 혼합 용액

- 2. Etch Parameter

- Etch Rate 식각 속도

- 일정시간동안 막질을 얼만큼 제거할 수 있는지를 의미

- 표면 반응에 필요한 반응성 원자와 이온의 양, 이온이 가진 에너지에 의해서 변화

- 플라즈마 상태의 원자와 이온의 양, 이온이 가진 에너지 등에 따라 식각 속도가 변동

- Control : concentration, agitation, etchant temperature, etched film density

- Etch Rate(E/R) = △T(식각 두께) / 식각 진행 시간 t

- Selectivity 선택비

- 다른 물질들 간의 식각률 차이의 비율

- 패턴 되는 식각에서 매우 중요한 변수

- 감광막과 그 아래 물질과의 식각률 비율

- Etch Uniformity 식각 균일도

- 전체적으로 얼마나 균일하게 식각되는가

- 회로의 각 부분마다 식각된 정도가 다르다면 특정 부위에서 칩이 동작하지 않을 수 있음

- 생산성 향상과 직결 : 플라즈마의 균일성, 챔버 내 환경 균일성이 필요

- Etch rate uniformity (%) = (max.etch rate - min. etch rate) / (max. etch rate + min. etch rate) * 100%

- FET들이 미세하면 미세할수록 안깎임

- Etch Profile 형상 & Etch Bias

- Etch profile often critical for structure application

- minimum edge loss for nano structure

- Slope edge for step coverage

- Etch profile often critical for structure application

- Plasma-induced Damage

- 표면에 데미지 → 열처리를 해줌

- Uncontrolled pattern-dependent etch rate modification and physical damage of the etching pattern

- CCP의 경우, 플라즈마 고밀도화를 위해 높은 전력 사용, 기판 전압의 증가로 이온 에너지 증가하며 기판 손상

- Etch Rate 식각 속도

- 3. Wet and Dry Etching

| Wet | Dry | |

| Method | chemical solutions | Ion bombardment or chemical reactive |

| Environment and Equipment | Atmosphere, Bath | Vacuum Chamber |

| Advantage | 1) Low cost, easy to implement 2) High etching rate 3) Good selectivity for most materials |

1) Capable of defining small feature size (<100nm) |

| Disadvantage | 1) Inadequate for defining feature size < 1um 2) Potential of chemical handling hazards 3) Wafer contamination issues |

1) High cost, hard to implement 2) low throughput 3) Poor selectivity 4) Potential radiation |

| Directionality | Isotropic (Except for etching Crystalline Materials) |

Anisotropic |

- 1) Wet Etching Process

- 액체 상태의 화학적 용액 또는 기상(Vapor)을 이용 화학적인 반응을 통해 식각하는 방법

- 식각 속도 (Etch Rate)가 빠르며, 선택비(Selectivity) 우수

- 건식 식각에 비해 상대적으로 정확성이 낮고, 식각에 사용한 화학 물질로 인해 오염 문제가 발생

- 등방성 식각 특성

- 2um 이하의 미세 공정에서는 패턴 형성이 불가능

- 박막의 전면 식각 또는 완전 제거(Strip)에 사용

- Batch 형태의 Wet Station 자비 사용으로 생산성이 높음

- 박막 표면으로 반응

- 화학 물질로 웨이퍼 오염 발생 원인

- 실리콘 결정 방향에 크게 영향 받으며 밀도가 높은 결정 방향이 낮은 식각 속도를 가짐 (식각 속도 [100] >> [111] 약 700배

- SiO2 식각에는 희석된 Diluted HF 사용

- 2) Dry Etching Process

- 1. Physical Sputtering (Ion Plasma Sputtering)

- 플라즈마 쉬스 전압으로 이온 가속, 가속 이온이 피식각물질에 부딪혀 물리적으로 떼어 내는 방식

- 2. Vapor phase Etching (화학적 식각)

- 플라즈마 내 활성종(Radical)을 식각제로 하여 화학반응을 통해 식각

- 3. Reactive Ion Etching (반응성 이온 식각)

- 화학적 식각과 스퍼터 식각 혼합, 식각률 개선 방식

- (1) Dry Etching Reaction Process

- Feed Gas로 플라즈마 형성에 의한 화학적 반응

- 반응 분자들이 웨이퍼로 확산되어 표면에 흡착

- 반응 발생 : Radical (식각 부분과 화학적 결합), Ion(물리적 충돌로 식각 부분의 원자 제거)

- 부산물(Byproduct)를 챔버 외부로 제거

- (2) Plasma Etch Reactors (Chambers)

- CCP (capacitive coupled plasma) Parallel Plate Reactor

- ICP (inductive coupled plasma) Barrel Plasma Etcher

- Downstream Etch System

- CCP Reactive Ion Etch

- 1. Physical Sputtering (Ion Plasma Sputtering)

- 3) 펄스 플라즈마 식각

- 소자 미세화로 기술적 난이도 증가

- 식각 균일도, 임계치수 제어, 식각 선택도, 식각 프로파일 확보, 식각 손상 등 발생

- 소스 전원 또는 바이어스에 펄스 파워 인가

- 식각 속도를 줄이지만 100%보다 데미지 덜 함.

- 빈시간에 세정을 하면 찌꺼기 제거 가능 → 식각 안정도 올라감

- ON 구간의 영향으로 식각률 감소

- OFF 구간의 영향으로 기판 손상 감소, 선택적 식각 가능

- 임계치수의 균일도 확보 등

- 제어가 잘 됨

- 4) Atomic Layer Etching (ALEt) 원자층 식각 기술

- nm 급의 게이트 산화막의 경우, RIE 공정 시 낮은 선택비로 실리콘 표면에 손상

- 자기 제한적인 표면 개질 단계 및 개질된 층의 제거 단계를 주기적으로 실행

- Multiple gate MOSFET & 3D architecture are implemented

- PALE(Plasma Atomic Layer Etching) 자기 제한 까지 시간 단축으로 생산성 향상

5. Ion Implantation & Diffusion

- Diffusion 확산

- 확산은 농도 차이에 의해 입자들이 이동하여 평형 상태에 이르는 과정

- 확산 공정이란 웨이퍼에 특정 불순물을 주입하여 반도체 소자 형성을 위한 특정 영역을 형성

- 화학반응을 통해 형성된 물질을 웨이퍼 상에 다양한 형태의 막 형성

- Diffusion Mechanisms

- Vacancy diffusion(공공형) 또는 치환형(Substitutional Diffusion)

- 기존 격자내의 원자가 존재하던 자리에 치환

- 반도체는 치환형 확산이 필여

- Interstitial diffusion is more rapid than vacancy diffusion (침입형)

- 불순물이 격자 내 원자와 원자 사이를 자유롭게 이동해 확산

- C, H, O

- Vacancy diffusion(공공형) 또는 치환형(Substitutional Diffusion)

- 확산과 이온 주입 비교

- Diffusion

- 웨이퍼 손상이 적음

- 일괄처리가 가능함

- 고온 공정 및 하드 마스트 사용

- 농도와 깊이 제어 어려움

- 동방성 이온 주입

- Ion Implantation

- 정확한 도핑량과 깊이 제어

- 농도와 접합 깊이 독립 제어

- 비등방성 이온 주입

- 이온 주입 후 표면 손상

- 채널링 현상 발생

- 고가의 장비

- Diffusion

- Ion Implantation

- Highly accuracy doping levels

- Depth profiles by controlling ion energy and channeling effects

- Recovery implant-damaged Si crystalline via thermal annealing

- Wider range of impurity species

- Low temperature operation

- Incident ion damage to semiconductor lattice

- Ion implantation equipment is expensive

- Ion Implanter Parameters

- Dose & Dopant species

- Dose is total number of ions implanted per unit area

- Over dose → amorphorization

- Range

- Ion Implantation is random process

- Projected range is peak of implanted profile

- Direct implantation of energetic ions into wafer

- Lattice Damage

- Implanted ions transfer energy to lattice atoms

- Freed atoms collide with other lattice atoms

- Free more lattice atoms

- Damages continues untill all freed atoms stop

- Damage can affect the results of subsequent processing steps

- Damage oxide layers etch faster than undisrupted oxide

- 가벼운 이온은 깊이 들어가고 무거운 이온은 표면만 깨지고 깊게는 못들어감 →질량을 조절해 깊이 조절

- Ion Stopping 정지 메카니즘

- Nuclear stopping (핵정지) : interaction between ion and lattice atoms

- Function of impact parameter and masses

- Scattered significantly and cause crystal damage

- Electronic stopping (전자정지) : inelastic collision with electrons of lattice atoms (High energy in wafer surface)

- Energy transfer is very small and deep penetration

- Negligible crystal structure damage

- Electronic stopping excitation creates heat

- Nuclear stopping (핵정지) : interaction between ion and lattice atoms

- Channeling 채널링

- 원자의 격자간 빈 공간을 따라 이온이 주입

- 레시피에서 예상한 깊이 이상으로 이온이 주입

- 원치 않는 농도 프로파일이 형성됨

- 웨이퍼를 7도 기울이고 (Tilt), 20도 정도 돌려(Twist) 이온 주입

- 이온 주입 전 희생 산화막을 성장시켜 사용 (공정 단계를 하나 더 추가)

- 이온 주입 전 실리콘 등을 주입하여 비정질화 허여 채널링을 방지 (공정 단계를 하나 더 추가)

- Dose & Dopant species

- Ion Source

- 진공 챔버에 반응가스 주입으로 플라즈마 형성

- 플라즈마를 형성하여 주입할 이온을 생성

- 전압을 음으로 강하게 걸어 양이온들만 전기장에 의해 추출함

- Ion Implanter Operation (이온 주입 장치)

- Annealing

- 분자 구조의 안정화, 불필요한 불순물 확산 방지

- 도전성 확보(낮은 비저항)

- Batch Furnace (>180nm) → RTP (Rapid Thermal Process, 급속열처리) (>65nm) → 웨이퍼 전체 열전달로 소자 및 회로 손상 우려 (미세화에 한계)

- 레이저 어닐링 공정 도입

6. Metallization (금속 배선)

- Electrically connection by Deposition (BEOL)

- Four common structure : Contact, Via, Plug, Interconnector

- Low resistivity and low resistant ohmic contacts

- Stable for long term operation

- Silicide, Metal plugs

- Metal Materials

- Conductivity decrease with rise in temperature

- Obeys Ohm's law

- Making alloy with another metal decrease conductivity

- Metal is independent of applied potential difference

- Silver, Copper, Aluminum, Gold, Tungsten, Alloys (Al-Cu)

- Barrier Metal Layer

- Aluminum과 Copper의 Insulating Layer와 반응 - 오염 발생

- 구리의 확산방지막 Diffusion barrier의 역할

- Good adhesion by chemical bonding

- Tantalum Barrier

- Ohmic Contact Structure

- Schottky Contact in metallization (Work function of materials)

- One-way conducting, with the other way off

- 물질간 접합 후 에너지 장벽이 높아져 캐리어의 이동이 어려움

- Ohmic Contact

- Two-way conducting

- 물질 간 접합 후 에너지 장벽이 거의 없어 캐리어의 이동이 쉬움

- Schottky Contact in metallization (Work function of materials)

- Aluminum : Junction Spiking

- Electromigration (Hillock & Void)

- Copper

- Reduction in resistivity

- Reduction in power consumption

- Superior resistance to electromigration

- Difficult dry etching

- 20~30% fewer process steps (Damascene & Electroplating)

- 7nm 급 구리 배선의 촉매(Seed)으로 Ru(루테늄) 사용

- Tungsten(W)

- 오늘날의 가장 진보된 칩은 100nm^2의 다이 크기에서 20억 개의 트랜지스터를 패키징

- 트랜지스터가 세 개의 터미널 장치인 것을 고려하면, 트랜지스터에 대한 60억 개의 접점이 스택 배선의 10-15 층에 연결

- 배선이 구리지만, 트랜지스터 레벨의 접점과 접점 레벨 바로 위에 있는 로컬 상호 연결 레벨은 텅스텐

- 텅스텐은 구리보다 약간 높은 저항을 가지지만 트랜지스터를 죽이는 구리 오염의 위험에 여전히 텅스텐이 사용

7. CMP (평탄화)

- Chemical Mechanical Planarization

- Aluminum interonnects : deposition & etching of metal layer

- Copper can't easily be removed chemical Etching

- Copper CMP technology was developed as a replacement

- Emerging applications, such as 3D memory structures

- Without CMP - 초점 심도가 다 달라짐 (패턴을 만들고 나면 엉망됨!)

- CMP 주요 공정 변수

- 평탄도 (Planarity)

- 균일성 (Uniformity, 1 sigma %)

- 연마 속도 (Polishing or Removal Rate)

- Dishing & Erosion

- Defect

- CMP Application

- STI 산화물 연마 공정 (STI Oxide Polish)

- LI (Local Interconnect) 산화물 연마 (LI Oxide Polish)

- LI 텅스텐 연마 (LI Tungsten Polish)

- ILD 산화물 연마 (ILD Oxide Polish)

- 텅스텐 플러그 연마 (Tungsten Plug Polish)

- 이중 다마신 구리 연마 (Dual-Damascene Copper Polish)

- CMP Quality

- Metal Layer Thickness Change

- Dielectric Leveling Change (Dielectric Thickness Change)

- Defect & Scratch by CMP Slurry Particle Contamination

- Self-stopping by Buffing CMP

- Final surface treatment by Dry Etching

- HSS (High Selectivity Slurry)

- Study Preston Equation

- CMP Slurry에 의한 공정 분류

- Oxide Slurry CMP 공정 : Cook의 연마 이론이 일반적으로적용

- Cerium Slurry CMP 공정 : Ceria Slurry는 약 180 ~ 350nm 크기의 Ceria Abrasive(CeO2, 산화세륨) 함류, STI 사용

- Poly Silicon Slurry CMP 공정 : Alumina 입자부터 Fumed 또는 Colloidal Silica Abrasive를 특수한 Chemical로 표면처리 후 초순수에 현탁하여 pH 7의 중성 특성

- Tungsten Slurry CMP 공정 : Kaufuman Model, 산화제가 금속막 표면을 산화시키고, 산화된 금속막 표면을 연마제의 물리적 마찰에 의해 제거해내는 반응이 반복해서 발생함으로써 연마가 진행

- Copper Slurry CMP 공정 : Cu Corrosion 문제로 인해 Slurry 제조 업체별로 산화제 및 Corrosion 방지용 성분 차이, BTA Chemical과 같은 부식방지제를 적용

8. Clean (세정)

- Wafer Cleaning 목적 및 기술

- 미립자, 유기 금속, 그리고 자연 산화물들과 같은 모든 웨이퍼 표면의 오염물질을 습식 방식으로 제거하는 세정

- 실리콘 웨이퍼의 수율은 웨이퍼 상에서 행해지는 처리로부터의 결함 밀도 (청정도 및 입자 수)와 반비례

- 작은 입자는 입자와 웨이퍼 기판 사이에 강한 정전기력이 존재하기 때문에 제거하기 어려움

- 표준 웨이퍼 클리닝에 사용된 화학 물질은 지난 30년 동안 크게 변하지 않음

- 산성 과산화수소 및 수산화 암모늄 용액을 사용하는 RCA 클린 공정을 사용

- 최근 오존 세정 및 메가 소닉 세정 시스템을 최적화 된 세정 기술과 함께 구현

- Wafer Cleaning Step

| Step | Purpose |

| Pre-Diffusion | 금속, 미립자 및 유기 오염 물질이 없는 표면 형성 경우에 따라 자연 산화물 또는 화학 산화물을 제거 |

| Metallic Ion Removal | 장치 작동에 해로운 영향을 줄 수 있는 금속 이온 제거 |

| Particle Removal | 메가 소닉(Megasonic) 세척 등, 화학적 또는 기계적 세정을 사용하여 표면에서 입자를 제거 |

| Post Etch | 에칭 공정 후 남은 포토 레지스트와 폴리머를 제거 "Etch Polymer"를 포함한 PR 및 고체 잔류물 제거 |

| Film Removal | 실리콘 질화물 etching/strip, 산화물 etching/strip, 실리콘 etching 및 금속 etching/strip |

3. Cleaning Process

- Wet Cleaning

- Chemical Cleaning : RCA Clean (SC1 Clean, SC2 Clean)

- Mechanical Cleaning : Megasonic, Poly-Vinyl Acetate Brush Scrubber

- 습식 세정 화학 물질

| 오염물질 | 이름 | 화학적 혼합물의 설명 (모든 세정은 DI 물 헹굼액을 따름) |

| 미립자 | Piranha (SPM) | 황산, 과산하수소, DI 물 |

| SC-1 (APM) | 암모니아산, 과산화수소, DI 물 | |

| 유기체 | SC - 1 (APM) | 암모니아산, 과산화수소, DI 물 |

| 금속 (구리 제외) |

SC - 2 (HPM) | 염산, 과산화수소, DI 물 |

| Piranha (SPM) | 황산, 과산화수소, DI 물 | |

| DHF | 플루오르화산, 수용액 (구리는 제거하지 않을 것임) |

|

| 자연 산화물 | DHF | 플루오르화산, 수용액 (구리는 제거하지 않을 것임) |

| BHF | 중화 플루오르화산 |

- RCA Cleaning Process (산업 표준 습식 세정 과정)

- RCA Cleaning

- Standard Clean - 1 (SC-1) : 암모니아수(NH4OH), 과산화수소(H2O2), 물(H2O)을 일정한 비율로 혼합하여 75 ~ 90ºC에서 미립자와 유기물질을 제거하기 위한 알칼리성 용액

- Standard Clean - 2 (SC-2) : 염산(HCl), 과산화수소(H2O2), 물(H2O)을 일정한 비율로 혼합하여 75~90ºC에서 금속성 물질을 제거하기 위한 용액

- Modification SC-1 / SC-2 : RCA 세정보다 더 높은 수준의 세정을 위한 화학 물질의 구성 및 비율 변형으로서 대표적으로 피라냐 세정, 불산 세정

- Piranha Cleaning : 황산(H2SO4), 과산화수소(H2O2), 물(H2O)을 일정한 비율로 혼합하여 90~130ºC에서 유기물질과 금속 불순물을 제거하기 위한 용액

- HF Cleaning : 물에 희석하여 사용하며 25ºC에서 산화막을 제거하기 위한 용액으로서 불산 세정을 한 웨이퍼의 표면은 공기 중에서 재산화에 대한 높은 안정적인 저항성

- RCA Cleaning

- Megasonic Cleaning

- 1 MHz 정도의 주파수를 이용한 초음파 에너지로 세정하는 공정으로서 아주 작은 미립자에도 에너지를 전달하여 제거

- Spray Cleaning

- 회전하는 밀봉된 챔버에 웨이퍼 카세트가 놓이고 습식 세정 물질이 웨이퍼 위로 스프레이 되어 오염 물질과 반응하여 떨어져 나온 후 DI water를 스프레이 하여 깨끗이 제거하는 방식

- Scrubber Cleaning

- 회전하는 스크럽 브러쉬를 이용하여 웨이퍼 표면의 미립자를 제거하는 세정 방법

- Wafer Rinse

- Overflow Rinse : 계속해서 DI water를 공급하여 Bath 밖으로 DI water를 배출하면서 헹구는 세정

- Dump Rinse : DI water가 탱크를 채우는 동안 웨이퍼에 스프레이 되면서 세정하는 방법

3. Dry Cleaning

- 유해한 화학 약품을 사용하지 않고 기상 상태나 가스 상태로 세정

- UV, O3 Cleaning : 150 ~ 600nm UV로 유기물(Polymer) 제거 공정

- Plasma Cleaning : Sputtering과 유사, Native Oxide 제거

- HF Vapor Cleaning : 세정액을 증발시켜 오염물질 분리 하는 세정

- 1일차 오후 이론 교육 정리 마침. (오타 있을 수 있지만 개인적인 정리 용으로 계속 복습할 예정!!)

반응형

'대외활동 > 반도체 공정 실습' 카테고리의 다른 글

| [엔지닉 X 인하대학교] 반도체 공정 실습 - 3일차 (2) (0) | 2023.07.02 |

|---|---|

| [엔지닉 X 인하대학교] 반도체 공정 실습 - 3일차 (1) (0) | 2023.07.02 |

| [엔지닉 X 인하대학교] 반도체 공정 실습 - 2일차 (2) (0) | 2023.07.02 |

| [엔지닉 X 인하대학교] 반도체 공정 실습 - 2일차 (1) (0) | 2023.07.02 |

| [엔지닉 X 인하대학교] 반도체 공정 실습 - 1일차 (1) (0) | 2023.07.01 |